You can pick these up for a few dollars on eBay: 4008 4-bit full adder pinout. The left shift by 2 places means multiplication by 4. So we will cheat and use a 4008 4-bit adder IC. Verilog provides a left shift operator using << to shift the bits to the left.

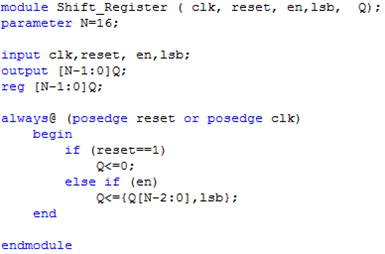

710 labs persy rosin lafayette county ms grand jury schedule. Unfortunately, for the 4-bit ALU, it would be impractical to use discrete chips to create a 4-bit adder. A Verilog HDL synthesis attribute that directs Analysis & Synthesis to implement input, output, and output enable registers in I/O cells that have fast, direct connections to an I/O pin, when possible. The testbench Verilog code for the ALU is also provided for simulation. ii) Write a Verilog description along with the test bench for a 4-bit ripple-carry adder using behavioral modeling. Today, fpga4student presents the Verilog code for the ALU. Full VHDL code for the ALU was presented.

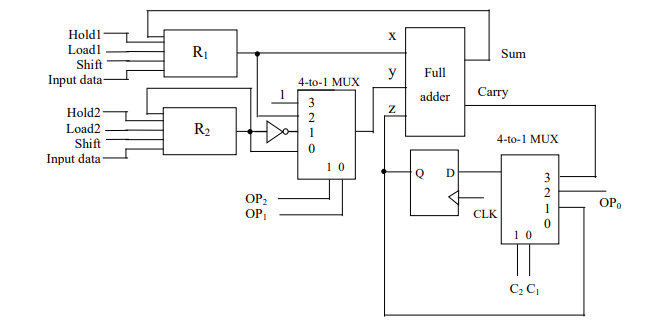

Verilog > support two dimensional arrays which are used in Memory modeling.A memory design will have one multi-bit port to read the data and one multi-bit port to write the data. condition for overflow: //-the ALU is performing addition or subtraction (ALUControl1 = 0) //-A and Sum have opposite signs, as detected by the XOR gate //-either A and B have the same sign and the adder is performing addition (ALUControl0 = 0) or A and B have opposite signs and the adder is performing subtraction (ALUControl0 = 1). A full adder made by using two half adders and an OR gate. Verilog code for Arithmetic Logic Unit (ALU) Last time, an Arithmetic Logic Unit ( ALU) is designed and implemented in VHDL. Clearly show all the waveform to get full credit.

0 kommentar(er)

0 kommentar(er)